# 전치왜곡방식을 이용한 선형 전력증폭기 설계

허 광 삼\*·문 성 익\*·양 두 영\*\*

# Design of the Linear Power Amplifier using the Predistortion Method

Kwang-Sam Heo\*, Seong-Ig Moon\* and Doo-Yeong Yang\*\*

#### ABSTRACT

This paper deals with designing the linear power amplifier using MESFET and Schottky diode. The power amplifier is designed to be ensure 3-W linear output using MESFET, and made up of 3-stage class-AB amplifiers in cascade. By choosing the final stage as the balanced structure, the output linearity is enhanced. The balanced structure of amplifier is composed of the Wilkinson power divider and combiner. In the designed 3-stage amplifier, when the input power is lower than -5dBm, power gain is 38dB. And it rapidly decreases as the input power increases larger than -5dBm. Therefore, to compensate for decreasing the gain, pre-distorter circuit is inserted in front of 3-stage amplifier. The pre-distorter is implemented using parallel Schottky diode. The optimized linear power amplifier is composed of these pre-distorter and 3-stage power amplifier. As a result, when the maximum input power is 9dBm, the 1-dB gain compression point of linear power amplifier.  $P_{1dB}$ , is 37.61dBm

Key words: Linear power amplifier, pre-distorter

### 1. 서 론

최근 디지틀 방식의 이동 통신 시스템이 확산되면서 주파수의 사용 효율성을 높이는 선형 변조 방식에 대한 연구가 활발히 진행되고 있다. 이러한 선형 변조 방식은 정해진 출력 및 주파수, 온도 범위 내에서 선형성을 보장하는 선형 전력 중폭기(LPA. linearized

power amplifier)를 필요로 한다. 전력 증폭기의 선형화 방식으로는 데이터 전치왜곡(predistortion)에 의한 방식, 피드포워드(feedforward) 방식, 아날로그 전치왜곡 방식 등이 주로 사용된다. 데이터 전치왜곡 방식은 베이스 밴드 신호의 진폭 및 위상을 IF (intermediate frequency)또는 RF(radio frequency) 변조 이전에 모뎀 내에서 디지를 신호 처리 방법을 이용하여 중폭기의 복소 이득 전달 함수의 역함수로 사전 왜곡하는 방식이다<sup>1,5)</sup>. 이 방법은 디지를 기술을 사용하므로 적응 신호 처리 방식에 있어서는 타 방식에 비해 상대적으로 용이하다. 그러나 오차 신호를 검출하기 위한 복조과정이 필요하고 최종 출력 단에

<sup>&</sup>quot; 제주대학교 대학원

Graduate School, Cheju Nat, I Univ.

제주대학교 통신컴퓨터 공학부, 산업기술연구소, 정보통신연구소 Faculty of Telecommunication & Computer Eng., Res. Inst. Ind. Tech., Res. Inst. of Information & Telecommunication, Cheju Nat'l Univ.

서 다수 캐리어의 변화에 대한 보상이 어렵다.

피드포워드 LPA는 비선형 전력 증폭기의 출력으로부터 비선형 신호만을 검출하여 출력 신호에서 이를 상쇄하는 방식으로서 1970년대부터 마이크로파 통신이나 계측 시스템 등에 활용되어 왔다<sup>2.41</sup>. 피드포워드 방식의 선형화 회로는 다른 선형화 방식에 비해 선형화 정도가 매우 크다는 장점을 가지고 있다. 그러나 피드포워드 증폭기는 주 신호에 비해 매우 작은 오차 신호를 처리해야 하고 그 구조가 개방 루프 형태이므로 각 소자의 특성 및 시간적 변화에 의한 시스템 특성의 변화가 민감하다는 단점을 가지고 있다.

아날로그 전치왜곡에 의한 선형화 방식은 IF단 또는 RF단에서 비선형 중폭기의 입력신호를 사전 왜곡시킴으로써 선형화 특성을 구현하는 방식이다<sup>31</sup>. 이 방법은 소자 특성의 한계로 인해 선형성에 한계가 있으나, 주 중폭기 이외의 부가 중폭기가 필요하지 않아 피드포워드 방식에 비해 전력효율이 높은 장점이었다. 따라서 본 논문에서는 아날로그 전치왜곡 방식에 의한 선형 전력 중폭기를 설계한다.

#### 비 선형 전력증폭기 설계 이론

#### 2.1. 전력증폭기

전력중폭기는 입력의 RF신호를 중폭하여 고출력전력을 내는 일종의 변환회로로서, 소자의 선형영역뿐만 아니라 비선형영역까지 동작하는 중폭기이다. 전력중폭기의 입력전력( $P_{in}$ ). 공급전력( $P_{dc}$ ). 출력전력( $P_{out}$ )과 이득(G) 및 전력 참가 효율(PAE)의 관계는

$$G = \frac{P_{out}}{P_{in}} = P_{out}(dBm) - P_{in}(dBm)$$

(1)

$$PAE = \frac{P_{out} - P_{in}}{P_{ci}} = \frac{P_{out}}{P_{ci}} \left(1 - \frac{1}{G}\right) \tag{2}$$

이다

전력중폭기의 경우 입력전력이 중가하면 출력전력 도 선형적으로 비례하여 중가하지만 일정한 입력전력 이상에서는 입력이 중가하여도 출력전력이 선형적으로 중가하지 않는다. 이때 중폭기의 이득이 선형영역보다 1dB 작아지는 지점을 1dB 이득 압축점( $P_{1dB}$ )이라 하다 $^{6}$ .

전력증폭기는 소자에 가하는 동작점의 위치와 부하 특성에 따라 A급, B급 및 AB급으로 분류될 수 있다. A급 전력중폭기는 소자의 최대 채널전류와 드레인 항복전압의 중간지점에 동작점을 설정한 중폭기로 선 형성이 우수하고, 큰 이득을 얻을 수 있는 장점이 있 으나, 신호의 유무에 관계없이 일정의 전력을 소모하 여 효율이 떨어지는 단점이 있다. A급 중폭기의 최대 가능 효율은 50%이다. B급 전력증폭기는 소자의 핀 치-오프되는 점에 동작점을 설정하고, 부하 임피던스 를 고조파 성분에 대해서 단락시켜 기본파만 출력시 키는 중폭기이다. 입력신호가 없을 때는 DC 전력을 소모하지 않으므로 효율은 높지만, 핀치-오프에서 동 작하므로 출력신호의 왜곡이 중가하고, 이득이 감소 하게 된다. 이론적으로 B급 중폭기의 최대 효율은 78.5%이다. AB급 전력중폭기는 A급과 B급 중폭기의 중간형태로 전력이득과 효율이 최적화된 지점을 동작 점으로 선택한다. 동작점은 보통 A급과 B급의 사이 에 위치하게 된다.

#### 2.2. 증폭기의 선형화 방식

비선형 중폭기의 출력 특성은 입력의 멱급수 형태로 모델링할 수 있다. 그러므로 식(3)와 같은 정현파가 중폭기로 입력되었을 때. 출력 y(t)는 식(4)와 같이 나타내어진다.

$$x(t) = A\cos(\omega_1 t) \tag{3}$$

$$y(t) = \frac{1}{2} a_2 A^2 + (a_1 A + \frac{3}{4} a_3 A^3) \cos(\omega_1 t) + \frac{1}{2} a_2 A^2 \cos(2\omega_1 t) + \frac{1}{4} a_3 A^3 \cos(3\omega_1 t) + \dots$$

(4)

식(4)에서 나타낸 것처럼 출력에는 입력 주파수  $\omega_1$  이외에 dc,  $2\omega_1$ ,  $3\omega_1$  등의 고조파가 생겨난다. 또한  $a_3$ 가 0보다 작을 때. 기본파 출력 성분에서  $(a_1A+\frac{3}{4}\,a_3A^3)\cos(\omega_1t)$ 가  $a_1A\cos(\omega_1t)$ 보다 작

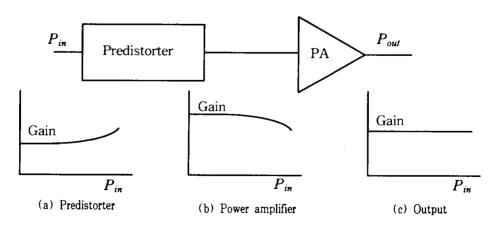

아짐을 볼 수 있는데 이는 입력이 증가함에 따라 이 득이 감소하는 AM-AM왜곡을 나타낸다. 즉 입력 성 분이 커질수록 기본파  $\omega_1$ 의 출력 성분 중 비선형성 이 커짐을 의미한다. 이러한 비선형성은 일정한 포락 선을 갖는 변조방식에서는 전체 시스템 특성에 그다 지 큰 영향을 주지 않지만, 현재 우리나라 PCS에 사 용되는 QPSK와 같은 포락선이 일정치 않은 변조방 식에서는 중요한 요소 중 하나로 고려되어진다. 따라 서 중폭기의 비선형성을 개선하기 위한 노력들이 다 양한 방법으로 연구되어 왔는데 그 방법을 구분지어 보면 크게 백오프(back-off), 피드백(feedback), 피드 포워드, 전치왜곡 방식으로 나뉜다. 이 중에서 전치왜 곡 방식은 진행파관(TWT)을 이용한 중폭방식에서부 터 최근의 HPA(High Power Amplifier)방식에 이르 기까지 중폭기의 비선형성을 보상해주기 위해 가장 널리 사용되어 오고 있는 방법이다. 전치왜곡 방식은 중폭기의 이득 변화에 반대가 되는 전치왜곡기를 중 폭기 앞단에 삽입함으로써 AM-AM왜곡을 보상해준 다. Fig. 1은 전치왜곡기를 이용한 중폭기의 선형화 방법을 보여주고 있다.

전력증폭기는 입력전력이 증가함에 따라 이득이 감소한다. 반대로 전치왜곡기는 입력전력이 증가하면 이득이 증가한다. 따라서 증폭기의 특성과 전치왜곡기의 특성을 더해주면 Fig. 1(c)와 같이 이득이 선형화된다.

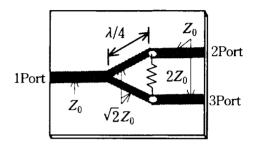

월킨슨 전력분배기는 X-band 이하 대역에서 주로 쓰이는데, 구조가 간단하며, 넓은 대역폭 및 높은 분 리도를 갖는 이점이 있다<sup>7)</sup>, 마이크로스트립 라인을 이용한 전력분배기의 구조를 Fig. 2에 나타내었다.

Fig. 2 The wilkinson power divider using microstrip line

윌킨슨 전력분배기에서 출력단자들이 모두 정합이 되면 입력전력은 각 출력단자로 절반씩 나누어지며 저항에서는 손실이 생기지 않는다. 그러나 출력단자가 정합되지 않는다면 반사되는 전력은 모두 저항에서 손실된다. 출력단자가 정합되었을 경우의 이상적인 S파라미터를 식(5)에 나타내었다.

$$\begin{bmatrix} S_{11} & S_{12} & S_{13} \\ S_{21} & S_{22} & S_{23} \\ S_{31} & S_{32} & S_{33} \end{bmatrix} = \begin{bmatrix} 0 & -\frac{j}{\sqrt{2}} & -\frac{j}{\sqrt{2}} \\ -\frac{j}{\sqrt{2}} & 0 & 0 \\ -\frac{j}{\sqrt{2}} & 0 & 0 \end{bmatrix}$$

(5)

#### 2.3 윌킨슨 전력분배기

Fig. 1 Linearization of the power amplifier using predistorter

Fig. 2에서 출력 두 단자를 입력으로 사용하면 전력 결합기로 사용되어진다.

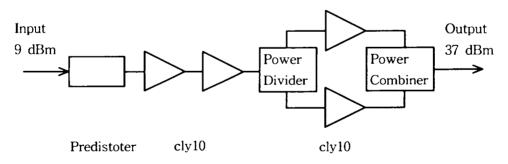

## Ⅲ. 선형 전력증폭기의 설계 및 결과

본 논문에서는 전치 왜곡방식을 이용하여 선형 전력증폭기를 설계한다. 전력증폭단은 simens사에서 개발한 Power GaAs FET인 cly10을 이용하여 AB급으로 설계하며, 출력전력을 높이기 위해 최종단은 평형구조로 구성한다. Fig. 3은 선형 전력증폭기의 구성도이다. Fig. 3에서 전치왜곡기는 증폭단의 앞단에 위치하게 된다. 설계에 있어서 전치왜곡기는 증폭기의 이득 특성과 반대의 특성을 갖도록 설계되어야 하기 때문에 증폭단 설계 후 전치왜곡기를 설계한다.

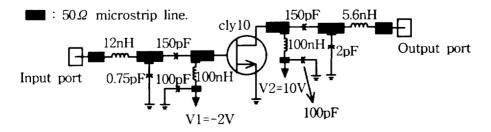

#### 31 증폭단 설계

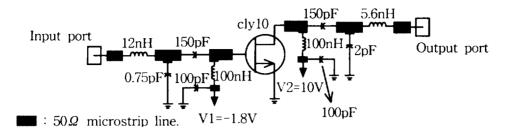

첫 번째 중폭단은 중폭기의 이득과 효율성을 고려 하여 AB급으로 중폭단을 설계하였다. 설계에 사용된 틀은 serenade를 이용하였으며, 사용된 소자는 simens 사의 cly10을 이용하였다. Fig. 4는 설계된 첫 번째 증폭단의 회로도이다.

중폭단의 동작점은  $V_{de}$  = 9.86V.  $I_{d}$  = 0.26A가 되도록 인가하였다. 설계 결과 입력전력이 10dBm이하일 때 12.5dB의 이득을 얻을 수 있었으며. 입력이 10dBm이상일 때는 입력전력이 커짐에 따라 이득이점차 감소하였다. 입·출력 정재파비는 모두 1.5이하로 설계하였다.

두 번째 중폭단 설계에 있어서는 좀 더 높은 전력을 수용하기 위하여, 동작점이  $V_{de} = 9.86$ V.  $I_{d} = 0.37$ A가 되도록 AB급으로 설계하였다. Fig. 4에서 동작점의 드레인 전류  $I_{d}$ 를 높여주기 위하여 V1=-1.8V로 인가하였다. 정합회로 또한 Fig. 4와 같이 설계하였으며, 마이크로스트립 라인의 길이를 가변적으로 취합으로써 최적의 특성을 얻어낼 수 있었다. 그 결과 입력전력이 10dBm이하일 때 약 12.7dB $\sim 12.9d$ B의 이득을 얻을 수 있었으며, 입력이 10dBm이상일 때는 입력전력이 커짐에 따라 이득이 감소하였다. 입·출력 정재파비는 모두 1.5이하로 설계하였다. 설계된

Fig. 3 Block diagram of the linear power amplifier

Fig. 4 The circuit of the first stage amplifier using MESFET cly10

Fig. 5 The circuit of the second stage amplifier

= :  $50\Omega$  microstrip line.

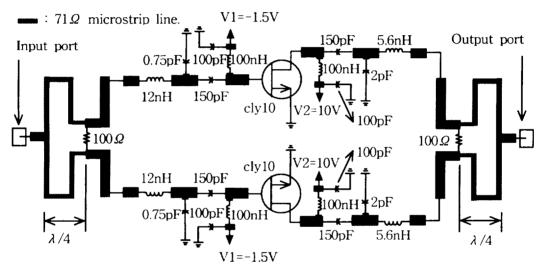

Fig. 6 The circuit of the final stage amplifier using balanced structure

두 번째 중폭단의 회로도를 Fig. 5에 나타내었다.

세 번째 중폭단은 출력의 선형성을 높이기 위하여 동작점이  $V_{dc} = 9.86$ V.  $I_d = 0.55$ A가 되도록 AB 급으로 설계하였으며. 평형구조를 취하였다. Fig. 5에서 동작점의 드레인 전류  $I_d$ 를 높여주기 위하여 V1=-1.5V로 인가하였으며 정합회로는 두 번째 중폭단에서와 같은 방식으로 구성하였다. 평형구조는 윌킨슨 전력분배기와 결합기를 이용하여 구성하였다. 윌킨슨 전력분배기는 입・출력간 -3.05dB의 전달특성과 모든 입・출력 단자에서 -30dB이하의 반사특성, 그리고 각 출력단자간 -40dB이하의 높은 분리도로 양호한 특성을 가지도록 설계하였다. 이렇게 설계된 세 번째 중폭단의 회로도를 Fig. 6에 나타내었다.

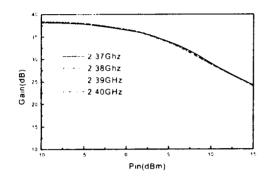

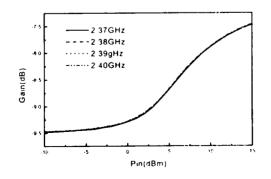

본 논문에서는 이렇게 설계된 중폭단을 가지고 중폭기를 3단으로 구성한다. 각 단의 결합 시 입·출력 포트는 모두 50 2으로 종단되었기 때문에 정합회로를 따로 구성할 필요가 없다. 이와 같은 설계방식은 앞단의 출력단과 뒷 단의 입력단에 직접 정합회로를 설계하는 경우보다 부피가 커지는 단점이 있으나 제작 및 회로 고장시에 각 단의 특성을 확인하는데 용이한 장점이 있다. Fig 7에 설계된 3단 전력증폭기의 이득특성을 나타내었다. 입력전력이 -5dBm이하일 때 38dB의 선형적인 이득을 가지고 있음을 볼 수 있으며, 입력이 -5dBm이상일 때는 입력전력이 커짐에 따라 점차 이득이 감소함을 볼 수 있다. 보통 증폭기의 선형영역은 소신호 이득보다 증폭기의 이득이 1dB작

아지는  $P_{1dB}$ 점을 기준으로 한다. 그러므로 이 증폭 기의 선혈적인 최대 출력은 입력이 -2dBm일 때. 37dB의 이득으로 3.16W(35dBm)가 얻어진다.

Fig. 7 Gain of 3-stage amplifiers

#### 3.2 전치왜곡기 설계

설계된 3단 중폭기의 이득특성과 서로 상쇄되어 좀 더 넓은 범위에서 선형적인 출력을 얻을 수 있도록

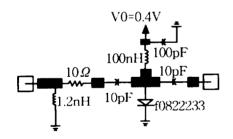

Fig. 8 The circuit of the pre-distorter using parallel diode

Fig. 9 Gain of the pre-distorter

전치왜곡기를 설계한다. 본 논문에서는 병렬 다이오드를 이용한 전치왜곡기를 설계하였으며 그 회로도는 Fig. 8에 나타내었다. 회로에 쓰인 Schottky다이오드는 hp사의 f0822233이다. Fig. 9는 설계한 전치왜곡회로의 이득 특성을 나타낸다. 전치 왜곡 회로의 이득특성을 살펴보면 입력전력이 -5dBm이하일 때 -9.5dB의 이득을 보이고 있으며, 입력이 -5dBm이상일 때는 입력전력이 커짐에 따라 이득 또한 커진다.

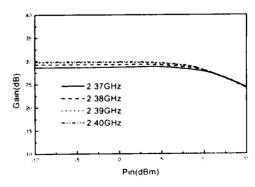

#### 3.3 선형 전력 증폭기 설계

본 논문에서는 3단으로 구성된 중폭기와 전치왜곡 기가 결합된 선형 전력중폭기를 최적 설계하였다. 이 렇게 설계된 선형 전력중폭기의 이득 특성을 Fig. 10 에 나타내었다. Fig. 10에서 살펴보면 입력이 5dBm이 하일 때 선형적인 이득 특성을 보이고 있다. 입력이 5dBm~9dBm의 범위에서는 입력전력이 커짐에 따라 이득특성이 완만하게 감소함을 볼 수 있으며, 입력전 력이 9dBm이상일 때는 이득이 급격하게 감소하고 있음을 볼 수 있다. 또한 중폭기의  $P_{1dB}$ 은 입력전력 이 9dBm일 때 나타났다. 그러므로 중폭기의 선형적 인 최대 출력은 입력이 9dBm일 때 28.05dB ~ 28.66dB 의 이득으로 약 5.3W(37.355dBm±0.305dB)룔 얻을 수 있다. 이를 Fig. 7에 선형화되기 전의 3단 전력증 폭기와 비교하여 보았을 때 선형 출력전력이 약 2.3dB 개선되었음을 알 수 있다. 주파수에 대한 이득 평탄도는 최대 ±0.61dB로 나타났다.

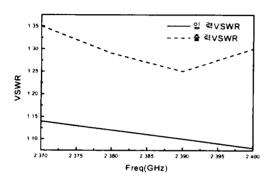

선형화된 전력증폭기의 입·출력 정재파비 특성을 Fig. 11에 나타내었다. Fig. 11에서 살펴보면 입력 정

Fig. 10 Gain of the linear power amplifier

재파비가 1.15이하. 출력 정재파비가 1.35이하로 모두 양호하게 나타났다.

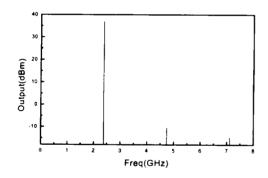

입력이 9dBm일 때 중폭기의 출력스펙트럼 성분을 Fig. 12에 나타내었다.

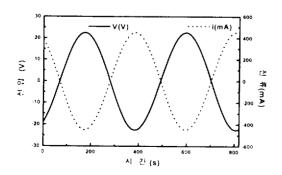

입력이 9dBm일 때 증폭기의 출력전압 및 전류파형은 Fig. 13과 같다.

Fig. 11 VSWR of the linear power amplifier

Fig. 12 The output spectrum where the input power is 9dBm

Fig. 13 The voltage and current wave where the input power is 9dBm

Fig. 13의 정현적인 전압·전류파형으로부터 출력에 왜곡이 없음을 알 수 있다.

#### N 결론

본 논문에서는 전력증폭기 소자인 MESFET cly10 과 Schottky 다이오드인 f0822233을 이용하여 5W급 의 선형 전력중폭기를 설계하였다. 우선 clv10을 이용 하여 3W의 선형적인 출력을 보장하는 AB급 증폭기 를 3단으로 구성하였으며. 이 **때** 출력의 선형성을 높 이고자 전력 중폭기의 최종단을 평형구조로 취하였 다. 중폭기의 평형구조는 윌킨슨 전력분배기와 결합 기를 사용하여 구성하였으며, 3단 평형 전력 증폭기 의 선형적인 이득 특성은 입력전력이 -5dBm이하일 때 38dB를 얻을 수 있었다. 중폭기의 왜곡을 보상하 는 방식으로는 병렬 다이오드를 이용한 전치왜곡방식 을 이용하였으며 소자는 Hp사의 f0822233 Schottky 다이오드를 사용하여 설계하였다. 전치왜곡기와 전력 중폭기를 합성하여 선형 전력중폭기를 얻을 수 있었 으며, 그 결과 입력전력이 9dBm일 때 28.05dB~ 28.66dB의 이득으로 최대 37.355dBm±0.305dB(5.07~ 5.8W)의 선형화된 출력전력을 얻을 수 있었다. 선형 전력중폭기의 입·출력 정재파비는 각각 입력측이 1.25이하. 출력측이 1.35이하로 모두 양호하게 나타났 다. 중폭기의 출력스펙트럼은 기본파 성분과 제 2 고 조파 성분간의 전력차가 47.49dBc로 나타났다.

# 참고문헌

- G. Karam and H. Sari. 1990. Data Predistortion Techniques Using Intersymbol Interpolation. IEEE Trans. on Comm. vol. 38. pp.1716-1723

- J. K. Cavers. 1995. Adaptation Behavior of a Feedforward Ampilfiers Linearizer. IEEE Trans. on Vehicular Tech., vol. 44, pp.31-40.

- 3) 윤장형. 1998. PCS용 선형 전력 증폭기의 설계 및 제작. 과학기술원 석사학위논문.

- 4) 백동현, 1998, 피드포워드 방식을 이용한 고주파

- 전력중폭기의 선형화 연구, 과학기술원 석사학위 논문.

- 5) 김남수의 3인. 1994. 적응 디지틀 전치왜곡기를 이 용한 선형화된 전력증폭기의 구현. 전자공학회지. pp.1625-1630.

- 6) Guillermo Gonzalez. 1984. Microwave Transistor Amplifiers Analysis and Design. Prentice-Hall. pp.180-356.

- David M. Pozar. 1993. Microwave Engineering. Addison-Wesley. pp.363-368.