# RTA방법에 의한 Pd- 실리사이드의 쇼트키 장벽 높이에 관한 연구

# 崔致圭, 李雲煥\*

Schottky Barrier Heights of Palladium Silicides

Formed by Rapid Thermal Annealing

Choi Chi-kyu, Lee Woon-hwan\*

#### Summary

Formation of the palladium silicides was performed by the rapid thermal annealing using quartz-halogen tungsten lamps. The Schottky-barrier heights of palladium silicides on both n-type (100) and (111) -oriented Si wafers have been measured in the temperature range 100-300K with use of a current-voltoge technique. Silicide formation was monitored by glancing-angle X-ray diffraction and AES.

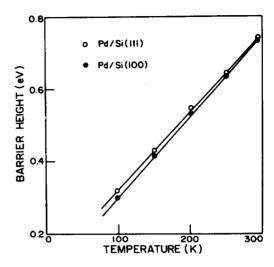

The values of the barrier heights are 0.32-0.74eV for Si(111) and 0.34-0.75eV for Si(100) at temperature in the range 100-300k.

The barrier heights depend primarily on the metal deposited and not on the particular silicide phase.

序論

전이 금속 실리사이드가 전기적 특성이 우수하고

층의 조성 및 두께가 균일하며 고체반응으로 형성되기 때문에 부착성이 좋을 뿐만 아니라 다른 금속과도 잘 부착한다. 일반적으로 실리사이드가 낮은 온도에서도 형성이 잘 되기 때문에 열처리중 소자의 다른

理工大學 助教授, 대구교육대학\*

특성들을 변화시키지 않으므로 VLSI(Very Large Scale Intergration) 에서 gate 전국 및 회로간 연결 물질로 크게 각광 받고 있다(Shenai, 1985).

금속- 반도체접합으로 그 계면에서 생겨나는 금속 실리사이드는 쇼트키 장벽이 형성된다. 따라서 쇼트 키 장벽 형성의 성질은 계면과 표면상태에 따라 크게 변화되며(Sze 1981, Bardeen 1947), Andrews와 Phillips은 처음으로 전이금속 실리사이드- 실리콘 계면의 장벽높이를 bulk실리사이드에 연관시킴으로써 화학적 결합의 중요성을 강조하였다(Andrews and Phillips, 1975).

그러나 Schmid등은 금속-실리콘 접합에서 interfacial bond의 성질들이 그 제면에서 구조적 그리고 화학적 조건을 만족시키기 위하여 bulk실리사이드의 성질로부터 수정되어야 한다고 제안했다(Schmid, 1983).

최근에는 NiSi, PtSi, TiSi등 많은 실리사이드 물질증 PdSi는 열역학적 및 화학적으로 안정된 물질로 알려져 있다( Tu, and Mayer, 1978). Pd-Si계는 Pd₂Si가 열역학적으로 낮은 온도에서 안정된 상을 가지며 PdSi상은 공융온도 820°C 이상에서도 일어나므로 공융 온도 부근에서 실리콘과 결합된 초기상태 Pd₂Si는 Pd₂Si+ Si 820°C→2PdSi로 반응하여 PdSi상으로 변형되어 안정된 상을 갖게 된다( Wei, 1985).

PdSi의 형성과 기본물성에 대하여 Ho등 많은 사람들에 의하여 최근에 많이 연구되고 있다( Ho, 1980, Ottaviani, 1981).

그러나 RTA( Rapid Thermal Annealing) 방법에 의한 Pd/Si계면에 생성되는 Pd실리사이드 쇼트키 장벽높이( Schottky Barrier Height) 는 규명되지 않았다.

따라서 본 연구에서는 전이금속들 중에서 비저항이 낮고, 고온에서도 안정하고, Si표면위에 native o xide가 있을 경우 실리사이드가 형성되지 않는 PdSi를 RTA방법으로 형성시키고, 쇼트키 다이오드를 제작하여 XRD로 형성된 PdSi의 상과 Auger 스펙트럼으로 Pd와 Si의 결합 조성비를 조사하였고, 순방향전류-전압특성곡선으로부터 쇼트키 장벽높이, ideality factor, 활성화에너지 등을 구하였다.

# 實驗 및 方法

### 1. Schottky Diode 제작

실리사이드 형성를 위하여 사용된 기판은 Dynamit Nobel사의 N형 실리콘 웨이퍼로서 비저항이 1.2~1.8Ω·cm이고 배향은 (100) 면과 비저항이 3~6.6Ω·cm이고 배향은 (111) 면으로 하였다. 중차물질인 Pd는 Johnson Matthey사의 순도 5N의 wire 였다. 먼저 실리콘 웨이퍼를 아세톤에 담구어 약 5분간 탈지시킨후에 탈이온수(비저항~20MΩ·cm)로 세척하고 H₂SQ,와 H₂Q₂를 1:1의 비율로 혼합한 용액에서 5분간 담구어 산화막을 형성한 다음 10%의 HF용액으로 etching시켰다. 표면이 깨끗해진 것을 확인하고 이물 탈이온수로 충분히 세척하여 건조한 아르곤가스로 불어서 건조시켰다. 이렇게 준비한 기판에는 native oxide가 잔존할 가능성이 있으므로 충착기내에서~50m torr의 Ar분위기에서 DC sputtering을 하여 잔류 산화막을 제거하였다.

Pd는 진공도가 ~10<sup>-6</sup> torr에서 중착하였다. Schottky diode 형태는 직경이 0.1mm와 0.5mm 원형으로 재작하였다. Pd 중착은 전자비임으로 중착율 1.5 Å/s으로 하여 1000 Å두께로 중착시켰다. 이때 사용한 도가니는 아루미나를 사용하였으며, 전자비임의 가속전압은 4KV, 필라멘트 전류는 50mA였고, 중착물은 INFICON XTM형의 thickness monitor로 수정진동자의 진동수로부터 구하였다.

#### 2. RTA

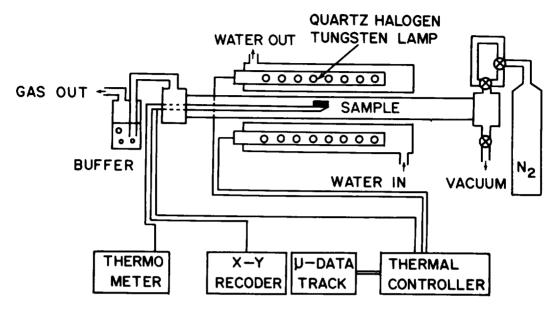

그림1은 본 실험에서 사용한 RTA 장치의 개략도이다. 이 장치의 구성은 annealing chamber와 thermal controller(Thermal Mode 6000 Temperature power controller)로 되어 있다. 외곽 chamber는 알루미늄으로 덩스텐 할로겐램프와 빈사경이 부착되어 있으며, 캠프의 최대전력 밀도는 26W/cm²로써 실험조건에 따라 임의로 전력밀도를 조절

Fig. 1 Schematic diagram of a RTA System.

할 수 있도록 하였다. 석영관 양단에는 질소가스를 가열시 최대 압력이 4psi가 되도록 하였으며, control ler는 μ data-track( Model 73211) 이 부차된 thermal controller thermometer로 구성되어 있다. 온도의 측정 및 재어는 C-A 열전대로부터 읽은 전 압을 thermal controller로 보내지면 controller에 내장된 프로그램에 따라 feed back 시킴으로써 온도를 조절할 수 있다.

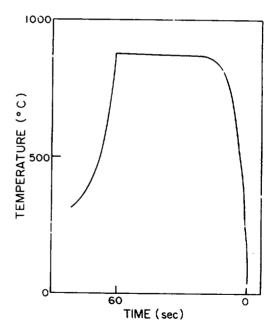

그림2는 X-Y기록계로 나타낸 전형적인 RTA장치의 온도 특성 곡선을 표시한다. 온도 900°C까지 올리는데 필요한 시간은 10초간이다. 따라서 본 실험에서는 Pd 실리사이드를 형성시키기 위하여 열처리 온도는 HO등이 규명한 PdSi상의 형성 최적조건에 따라 900°C로 20초간으로 하였다(Rubloff, 1981, Kim. 1987)

#### 3. 축정

형성된 실리사이드의 상을 조사하기 위하여 X - 선 회절분석기( Phillps사의 PW1710) 을 이용하였다. X - 선의 선원은 Ni를 filter로 한 CuKa로 그 파장은 1.5418Å이였고, 실험시 필라멘트 전류는 20mA, 가

Fig. 2 A typical temperature curve obtained by RTA.

속전압은 35KV, 검출기의 full scale은 2×10<sup>-3</sup>cps로 하였으며 scan영역은 20를 10°에서 80°범위로 하였다. 축각기내에 시료를 장치할때 기준면에 대하여 0.1m m의 오차가 있다면 회절이 일어나는 각도가 0.5°의 편차가 나오므로 시료장치시에 오차의 요인을 극소화 하도록 노력하였다.

형성된 Pd-실리사이드의 조성비를 조사하기 위하여 Auger 전자분광기(Auger Electron Spectroscopy; AES RIBER LAS-500 FRANCE)로 depth profile하였다. depth profile은 Ar ion sputtering으로 표면을 제거하면서 얻은 Auger 스펙트럼의 피이크-피이크간의 높이를 측정하여 이로부터 계산하였다. 미분형 Auger 스펙트럼은 CMA(cylindrical mirror analyzer) 외부 cylinder

에 2.2V 피이크- 피이크간의 정현파로서 변조시켜 line shape의 미소한 변화도 감지하도록 하였으며, 본 실험에서의 감지한계는 약 0.1%동도 정도였다. 또한 sputtering은 초기 진공도가 1.5×10° torr에서 이은펌프의 작동을 정지시키고 아르곤가스를 주입시켜 아르곤의 분압을 2×10° torr로 유지한 상태에서 sputtering을이 최소가 되도록 이은 gun을 작동시켰고, 자료를 얻을 때에 Auger 전자의 chemical effect 에 영향을 주지 않도록 노력하였으며, 30분 간격으로 titanium 숭화를 시켜 아르곤의 순도를 높였다. 표1은 AES자료를 얻을 때 Ar ion sputtering으로 depth profile할 때의 실험조건을 나타낸 것이다.

Table 1. Experimental condition for Auger/sputter profiling.

| base pressure                           | 3x10 <sup>-●</sup> Torr |

|-----------------------------------------|-------------------------|

| primary beam energy                     | 3000eV                  |

| emission current                        | 300u A                  |

| electron multiplier high voltage        | 2.5kV                   |

| lock-in amplifier amplitude sensitivity | lmV/sec                 |

| lock-in amplifier time constant         | 0.1 sec                 |

| scanning range                          | 0 – 540e V              |

| A'ion acceleration voltage              | 3kV                     |

| Ar partial pressure                     | 2x10 <sup>-5</sup> Torr |

| Ar gun filament current                 | 20mA                    |

쇼트키-다이오드에서 쇼트키-장벽높이(SBH) 값을 구하기 위하여 순방향 전류-전압 특성은 Γ΄ A Meter/DC Voltage Source(Model 4140(B HEWLETT PACKARD)를 사용하여 인가 전압을 10mV씩 변화시켜 300mV까지 측정하였다. 순방향 전류의 온도 의존성은 †에 대한 ln(Js/T²)의 Richardson plot로부터SBH값과 활성화 에너지를 계산할 수 있으므로(Aldert Vander Ziel, 1957) Air Protucts사의 Model DE-20 저은장치를 사용하여 전류-전압측정은도 범위를 100K에서 300K까지 하였다. 여기서 Js는 인가전압이 0 일때 포화전류밀도이다.

# 結果 및 考察

### 1. XRD

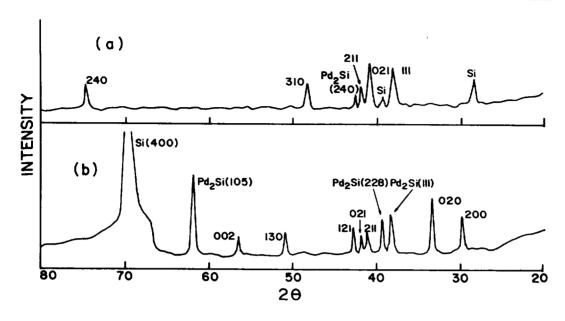

실리사이드는 매우 다양한 상이 있는 것으로 밝혀져 있다. 그림3은 Pd(1000 Å)/Si(111) 과 Pd(1000 Å/Si(100) 을 RTA방법에 의하여 900°C에서 20초간 열처리한 XRD 스펙트럼이다. Pd — 실리사이드들에 대한 피이크들이 20<20°인 위치에서는 나타나지 않아서 20°≤20≤80°인 범위에 대한 자료만을 분석 대상으로 하였다.

(b) 의 경우에서 대표적인 PdSi스펙트럼은 ortho mic구조를 가진 PdSi(020) 가 발견된다. 또한 Pd<sub>2</sub>Si 피이크가 나타나는 것은 Pd<sub>2</sub>Si상에서 PdSi상으로 진

Fig. 3 X-ray diffraction spectra of the samples processed by the RTA at 900°C for 20s;

(a) Pb on n-type Si(111) and (b) Pd on n-type Si(100).

행되는 도중 잔류되는 상으로 보여진다. Wei는 Rutherford Backscattering Spectroscopy(RBS) 실험에서 이와같은 것이 PdSi의 matrix속에 위치하거나, grain boundary 속에서 분리되었는지도 모른다고 추측하였다(Wek, 1978, Hall, 1972).

따라서 PdSi계에서 초기반응을 Pd<sub>2</sub>Si에서 실리콘과 점차반응되어 공용온도에서 2PdSi로 되기 때문에 750°C 이상에서 성장되는 PdSi마은 불연속성을 갖는 것으로 사료된다.

20 가 69.28에서 나타난 강력한 (400) 배향면의 실리콘 피이크는 원래 실리콘 기판의 배향면과 다르다. 이것은 시료에서 발견된 실리콘은 어떤 texture를 가지고 있다고 생각된다. (a) 의 경우는 Pd₂Si상의 (240) 면 이외에는 PdSi상으로 확인 되었다. 여기서 나타난 피이크의 강도는 Pd/Si(100) 보다 낮은 것은 실리콘과 Pd가 완전한 반응이 일어나지 않음을 알 수있다. 형성된 Pd-실리사이드 grain크기는 Seherre r의 공식 B= K λ/t·cos θ를 이용하여 X 선회절 스펙트럼으로부터 구할 수 있다(Cullity, 1978). 여기서 B는 grain의 크기, λ는 X-선의 과장, t는 라디안으

로 표현된 최대반치폭(full width half maximum; FWHM), θ는 Bragg각이다. 보정인자 k는 온도와 내부변형에 대한 함수이며 값은 약1이다. 따라서 본실험에서 형성된 Pd-실리사이드 grain 크기는 약150~200Å으로 나타났다.

#### 2. AES분석

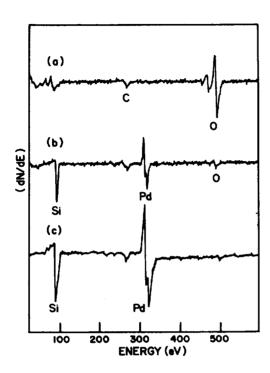

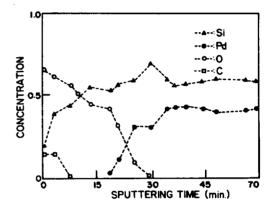

그림4는 RTA방법으로 열처리한 시료의 Auger 스펙트럼이다. (a)는 initial survey Auger 스펙트럼으로 열처리 중에 C와 O의 오염으로 Pd의 피이크는 모두 없어졌다. 단지 실리콘은 고온에서 O와 반응하여 SiOx의 형으로 변화하여 92eV에서 78eV로 편기되어 있으며 O의 양이 표견의 65%이상 차지하고 있다. (b)는 시료를 30분간 Ar ion sputtering을 행한 후에 얻은 Auger 스펙트럼으로 91eV에서는 실리콘의 주 피이크인 Si-L<sub>2.3</sub>L<sub>2.3</sub>VV 전이에 의한 피이크와 330ev에는 Pd의 주피이크인 Pd-MVV 전이에의한 피이크가 현저하게 나타난다. 503eV에는 O의주 피이크인 O-L<sub>2.3</sub>L<sub>2.3</sub>가 현저하게 줄었다.

Fig. 4 The Auger eletron Spectrum of the samples; (a) as prepared (b) and (c) during Ar ion sputtering C and O are the main impurities at the surface from (a).

이 그림에서 실리콘의 line shape로부터 실리사이 드의 특징 상에 대한 스펙트럼인지의 여부는 확실히 알수 없다. (c)는 시료를 70분간 Ar ion sputtering을 행한후에 얻은 Auger 스펙트럼으로 Si-L<sub>2.3</sub> W의 피이크의 모양이 원소상태의 line shapes도 아니고 Pd<sub>2</sub>Si 실리사이드에 의한 line shape도 아닌 독특한 모양을 하고 있다. sputtering 시간을 더 늘려 계속하여도 line shape의 모양이 변하지 않았으며 단지 조성은 Pd와 Si의 양이 거의 1:1로 나타났다. 이것은 PdSi의 특성 스펙트럼으로 생각된다. 이 스펙트럼으로부터 Pd와 Si의 농도는

$$A_i = \frac{\alpha_i I_i}{\sum_j \alpha_j I_j} = X_i$$

로 주어진다. 여기서  $A_i$ 는 규격화된 Auger 신호이고,  $\alpha$ 는 검출된 모든 원소에 대한 것이며,  $\alpha$  는 역 Auger

감도인자( inverse sensitivity factor) 로서  $\alpha_i I_i^0 = I_s^0$ 이다. 참자0는 순수한 원소를 나타내며, s는 임의로 서택된 표준원소를 나타낸다.

그림5는 Si와 Pd의 sputtering시간에 대하여 윗식으로부터 얻어진 농도를 나타낸 것이다. Pd와 Si의비가 Pd는 41.5% Si는 58.5%로써 그 조성은 PdSi에가까운 것임을 알 수 있다.

따라서 그림4의 (c)에서 91eV에 나타난 실리콘 스펙트럼이 line shape는 그 상이 PdSi인 경우에 대 한 미시구조를 나타내는 특성피이크로 생각할 수 있다.

Fig. 5 AES depth profile of the Sample annealed at 900°C for 20s by RTA.

The Concentration of Pd and Si are consistent with the PdSi Stoichimoetry.

#### 3. SBH

쇼트키 다이오드에서 열적 성질을 나타내는 전류 및 포화 전류 밀도 방정식, ideality factor(n) 등을 다음식으로 표현이 된다(Buckley, 1972).

$$J = J_s \left( \exp\left(\frac{qV}{n kT}\right) - 1 \right) \tag{1}$$

$$J_s = A^{**}T^2 \exp\left(-\frac{q\phi_{B_n}}{kT}\right) \tag{2}$$

$$n = (\frac{q}{kT} \frac{\partial V}{\partial (I_n J)})$$

(3)

여기서 포화 전류 밀도 Js는 인가전압이 0일 때 전류-전압특성곡선에서 외삽법에 의하여 얻어지며  $A^{**}$ 는 Richardson 상수, k는 Boltmann상수,  $\phi_{B_{\pi}}$ 은 쇼트키 장벽높이이다.

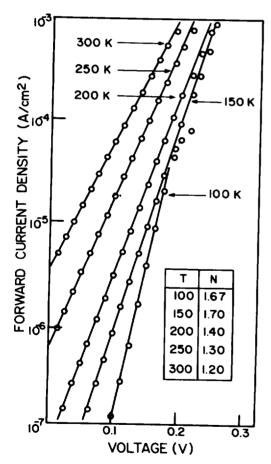

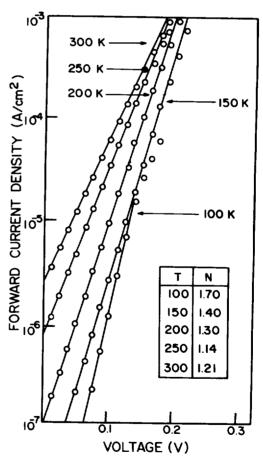

그림6과 그림7은 배향이 각각(111) 먼 및 (100) 면 인 실리콘기판에 대하여 측정온도 100~300K영역에서 나타낸 쇼트키 다이오드 순방향 전류~ 전압특성 곡선이다. 식(3)을 이용하여 구한 ideality factor n값의 변화는 측정온도가 낮아질수록 중가함을 보였으나 대체적으로 일반적인 값 1~2에 잘 만족하였다. 여기에서 n값이 1일 때는 전류가 거의 열이온 방출에

Fig. 6 Foward current density-voltage characteristics of Pd on n-type Si (111) as a function of measured temperatures.

의하여 형성된다. 그리고 n값이 1보다 점점 커감에 따라 접합장벽의 터널링현상으로 기여하는 전류가 중가하게 됨을 알 수 있다.

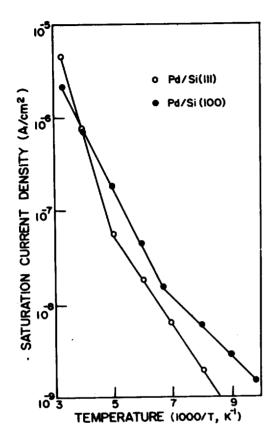

그림8에서는 인가전압이 0일 때 측정된 순방향 전류 밀도의 온도의존성을 나타내며 이 곡선의 기울기부터 활성화에너지 값을 산출할 수 있다.

Si(111) 면에 대한 활성화에너지는 온도가  $150\sim300$ K 범위에서는 2.5eV이고 온도가  $100\sim150$ K 범위에서는 0.99eV이다. 온도 150K에서 곡선의 기울기가 바뀌는 것은 온도 150K이하에는 depletion region에서 활성화에너지가 0.99eV로 재

Fig. 7 Foward current density-voltage characteristics of Pd on n-type Si (100) as a function of measured temperatures.

Fig. 8 Temperature dependence of saturation current density for n-type Si(111) and Si(100) at 100 K to 300 K.

결합에 의하여 전류가 흐르는 것이 지배적이며 온도 150K이상에서는 2.5eV의 활성화에너지를 가진 열전자 방출에 의하여 전류가 흐름을 의미한다. 또한 Si( 100) 면에 대한 활성화에너지는 온도 100~300K 범위에서는 0.5eV으로써 재결합에 의하여 전류가 흐르고, 온도가 200~300K 범위에서는 1.5eV 활성화에너지를 가진 열전자 방출에 의하여 전류가 흐른다. 이와 같은 특성은 다수전류가 열전자 방출에 기인되는 것으로 사료되며 저온영역에서 과도전류를 일으키는 재결합- 생성은 실리콘 표면 영역에 있는 deep level defect에 기인된다.

그림9는 측정온도에 따라 SBH를 나타낸 것이다. 그림6과 그림7에서 얻어지는 포화전류 Js값은 식(2)

Fig. 9. Change of the barrier height of Pd on n-type Si(111) and Si(100) as a function of measurement temperature at 100 K to 300 K.

를 사용해서 계산하면 Si(111) 면에 대한 SBH를 0.3 2eV에서 0.74eV로 측정되었고 (100) 면의 경우에는 0.34eV에서 0.74eV로 거의 선형적으로 온도에 대해 중가함을 알 수 있다.

# 摘 要

본 연구에서는 RTA방법에 의하여 Pd-Si계에서 우수한 Pd-Si가 형성됨을 확인하였으며 grain의 크기는 약 150~200Å으로 나타났다. AES 스펙럼인 분석에 의하여 Ar 이온으로 sputtering하면서 얻은 Pd와 Si의 조성비는 41.5%와 58.5%로써 Pd-실리사이드 상이 PdSi상에 거의 비슷함을 알수 있었으며, 91eV에서 나타난 line shape는 미시구조물 나타내는 PdSi의 특성 피이크임을 보였다. 100~300K의 온도 영역에서 측정한 전류-전압특성곡선으로부터 SBH 값은 0.32~0.75eV로 온도가 증가함에 따라 직선적으로 증가하였고 ideality factor n은 일반적인 값 1~2에 만족하였으며 고온영역에서는 거의 1에 근접

함을 Tu 등이 실험한 값과 거의 일치됨을 보였다( H erman 1983, Tu, 1981).

Si(111) 면에서는 100~150K온도범위, Si(100) 면에서는 100~200K 온도범위에서는 재결합 생성증 심에 의한 전류흐름을 보여 열처리시 defect를 제거 하는데 충분하지 못한다는 것을 알 수가 있었다. 따 라서 RTA방법에 의한 실리사이드 형성시 실리콘 표 면 영역에서 발생하는 defect를 재거하는 방법만 보 완시키면 PdSi접촉을 이용하는 어떤 바이폴라 집적 회로의 응용에도 가능하며 RTA는 장시간 열처리를 수반하는 전기로 열처리 방법보다 더 간편하고, 소자 의 다른 특성을 변화시키지 않으므로 전이금속 실리 사이드 형성에 우수한 장치로 평가되다.

# 引用文獻

- Aldert Vander ziel, 1957, Solid State Physical Electronics, Prentice-Hall, Inc, New York. 108.

- Andrews M. A, and Phillips J. C. 1975, Phys. Rev. Lett. 35, 56.

- Baradeen, J. 1947, Surface state and recitification at a metal-semiconductor contact, phys. Rev. 71, 717.

- Buckley. W. D. and Moss, S. C, 1972, Structure and Electrical characteristics of epitaxial Palladium Silicide contacts on Single Crystal Silicon and Diffused P-N Diodes, Solid-state Electronics, 15, 1331.

- Cullity. B. D. 1978, Elements of X-ray diffraction, Addison-Wesley, 102.

- Hall. P. M and J. M. Morabito, 1979. Matrix effects in quantitative Auger analysis of dilute alloys, Surface Sci. 83; 391.

- Herman F, 1983, Eletronic States and Schottky Barriers at Pd<sub>2</sub>Si/Si(111) Interfaces, Physica 117B and 118, B, 837.

- Ho, P. S., et. al., 1980, Chemical bonding and electronic structure of Pd<sub>2</sub>Si, Phys. Rev. B 22, 4784.

- Kim, K. H. et. al., 1987, The formation of Pd-silicides in Thin Ti-layer Sandwiched Pd/Si(111) System, JKPS. Phys. Soc., 20, 82.

- Otataviani G. et. el., 1981, Barrier heights and silicide formation for Ni. Pd and Pt on silicon, Phys. Rev., B 24, 3357.

- Rubloff. G. W. et. al., 1981, Chemical bonding and reaction at the Pd/Si interface, Phys. Rev. B 23, 4183.

- Schmid P. E. et. al., 1983, Effects of variations of silicide characteristics on the Schottky barrier heights of silicide—Si interface Phys. Rev. B 28, 4595.

- Shenai, K. 1985, Modeling and characterization of Dopant Redistributions in Metal and Silicide Contacts, IEEE Trans. on Electron Device, ED-32, 4.

- Sze, S. M. 1981 Physics of Semiconductor Devices, 2nd ed., New York Wiley

- Tu, K. N., 1981, Barrier Heights and Silicide Formation for Ni Pd and Pt on Silicon, Phys. Rev. B 24(6), 3354.

- Tu, K. N. and Mayer J. W., 1978, Thin Film Interdiffusion and Reactions, John Wiley and Sons Pre, Ch 10.

- Wei, C. S., J. Van der Spiegel, and Santiago, J., 1985, Characterizations of Palladium Silicides formed by Rapid Thermal Annealing, J Appl Phys. 58(11), 4200.